集成电路(IC)设计是现代电子工业的核心技术,它将复杂的电路系统集成在微小的硅片上,实现了电子产品的高性能、低功耗和小型化。本文以《集成电路设计实践》为切入点,探讨其核心流程、关键挑战与实践方法。

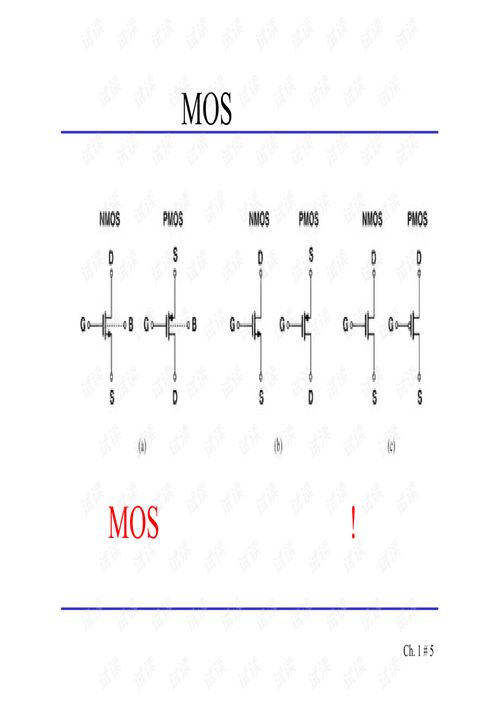

集成电路设计是一个系统性的工程,通常遵循自上而下的设计流程。它始于系统架构与功能定义,设计师需要根据产品需求,确定芯片的功能模块、性能指标和接口规范。随后进入前端设计阶段,即使用硬件描述语言(如Verilog或VHDL)进行寄存器传输级(RTL)建模与仿真,以验证逻辑功能的正确性。这一阶段强调设计的可读性、可复用性和可测试性,是确保芯片功能正确的基石。

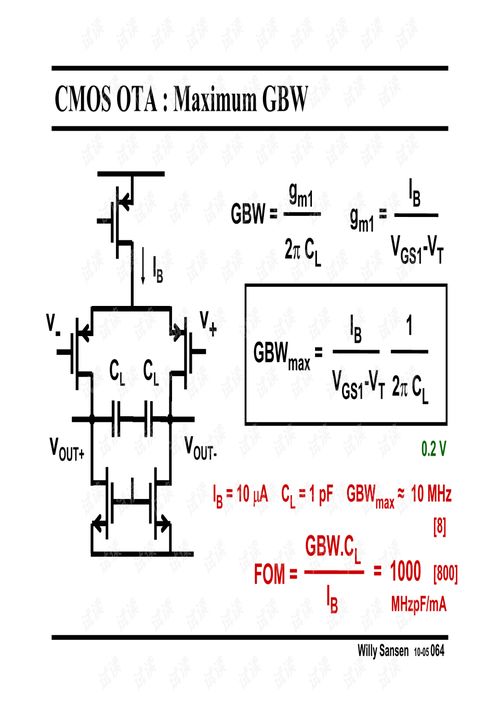

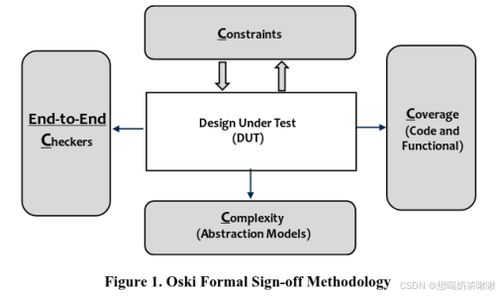

验证环节贯穿设计始终。除了功能仿真,形式验证、静态时序分析和功耗分析等工具被广泛应用,以提前发现潜在的设计缺陷。随着工艺节点不断微缩,物理效应的影响日益显著,使得设计与工艺的协同优化变得至关重要。

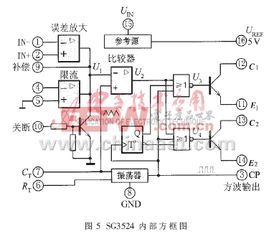

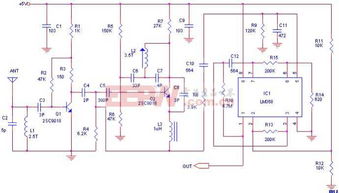

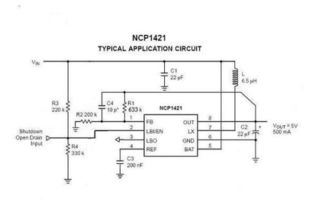

后端设计,即物理实现,是将逻辑网表转换为实际版图的过程。这包括布局规划、时钟树综合、布线与优化等步骤。设计师必须权衡面积、时序、功耗和信号完整性等多重约束,同时应对制造工艺带来的挑战,如光刻热点、电迁移和寄生效应。版图完成后,需经过设计规则检查(DRC)和版图与电路图一致性检查(LVS),确保其符合制造要求且与原始设计一致。

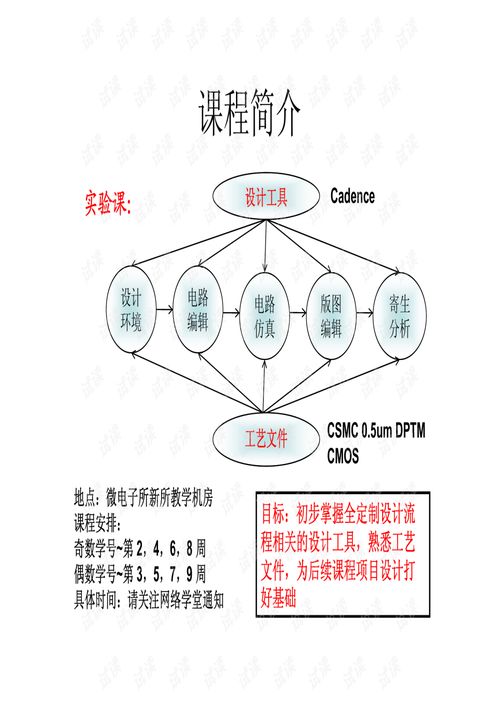

实践中的集成电路设计高度依赖电子设计自动化(EDA)工具链。从Synopsys、Cadence到Mentor Graphics等公司提供的软件平台,覆盖了从仿真、综合到验证的全流程。工具无法替代设计师的经验与创新。优秀的IC工程师不仅需要深厚的电路与系统知识,还需理解半导体物理、制造工艺乃至封装测试,才能在性能、成本与上市时间之间取得最佳平衡。

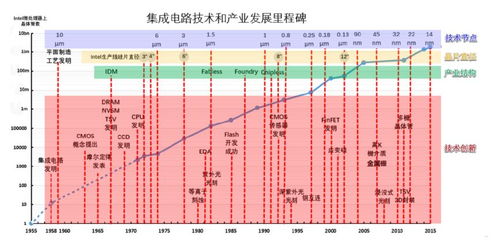

当前,集成电路设计正面临诸多新趋势与挑战。随着人工智能、5G和物联网的兴起,面向特定领域的架构(如AI加速器)需求激增,推动着软硬件协同设计的发展。先进工艺(如7纳米及以下)带来的量子效应与可靠性问题,要求设计方法学持续革新。开源EDA工具与RISC-V等开放指令集架构的兴起,正在降低设计门槛,促进创新生态的繁荣。

集成电路设计实践是一个融合了创造性思维与严谨工程的领域。它要求设计师在微观世界中构筑复杂系统,每一次流片都是理论与实践的交汇。随着技术演进,这一领域将继续驱动信息时代的革新,而深入掌握其核心实践,无疑是参与这场变革的关键。